PCIe从4.0发展到5.0,企业级SSD的性能标准从7GB/s变成了14GB/s。数据的爆发式增加,企业级SSD的容量需求越来越大,大容量SSD里面的NAND数量也在成倍增加。NAND数量越多,对信号带来的负载就越大;SSD的性能越高,对NAND实际达成的接口速率、信号完整性的要求也就越高。

如何充分发挥NAND性能,是打造高性能、大容量企业级SSD的重要课题。日前,Memblaze硬件开发高级总监倪勇在长江存储2022晶栈Xtacking线上沙龙企业级专场中,就NAND信号速率的提升和完整性方面的挑战,发表了主题演讲。

目前规模化量产的产品中,NAND接口速率可以做到1200MB/s左右,搭配8通道控制器刚好能够满足PCIe 4.0 SSD的前端带宽要求。而在下一代企业级SSD产品设计中,PCIe将升级至5.0,带宽翻倍,届时,NAND是否能够跑满2400MB/s的I/O速率,这将是SSD设计时需要着重考虑的问题。

1. Die外围电路设计带来的影响。

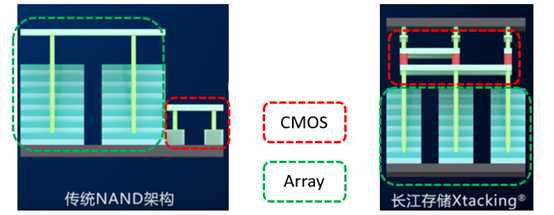

按照堆叠技术的不同,Die外围电路的设计主要有三种方式:CNA、CUA和CBA,其中,CNA存储单元与外围电路水平布局,技术成熟,简单易用。CUA、CBA存储单元与外围电路垂直立体布局,其制造工艺虽然更加复杂,但成品Die的面积更小,成本更低,由于外围电路与存储单元更近更直接,使得NAND可以实现更高的接口速率。

值得一提的是,长江存储的Xtacking架构,同样也是采用了外围电路与存储单元的垂直布局方式,其优势在于外围电路和存储单元晶圆可分开加工,通过晶圆键合技术将他们联接在一起,具有更高的技术难度和优势。

2. 多Die封装的NAND,Die的数量和堆叠方式也会影响接口速率。

以BGA132封装,包含2颗Die的NAND为例,通常NAND封装对外会暴露两组总线,即每个Die分别对应一组总线,分别是Bus0和Bus1,Die的堆叠方式按照其形状不同,也会分为两种,如图所示:

由于BGA132封装的外部信号总线分布位置是固定的,两种不同的Die堆叠方式在封装基板的设计上,会存在不同的布线长度。

3. NAND的封装尺寸与工艺,对NAND的信号速率的影响。

通过仿真模拟,我们比对了相同供应商、相同技术工艺、相同Die数量的NAND,其BGA154封装的仿真模型寄生参数只有BGA132的50%左右,这意味着,在控制器、拓扑和信号速率相同的前提下,使用BGA154可以获得更好的NAND信号眼图,带来更高的信号稳定性,同时,BGA154更小的尺寸也会为PCB的设计带来便利。

看完NAND,我们再来看下PCB设计方面,影响信号速率的几个关键点:

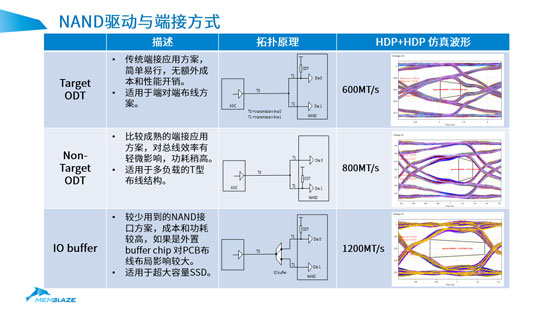

我们在同一个设计里面,做了三种不同的仿真拓扑,控制器相同,NAND数量一致(两颗16 Die的NAND挂在同一组总线上),布线长度接近的情况下,使用Target ODT能跑到600Mbps,Non-Target ODT可以达到800Mbps,如果使用IO buffer,无论内置还是外置,同样的NAND数量下,可以达到1200Mbps。这三种不同拓扑的效果一目了然。

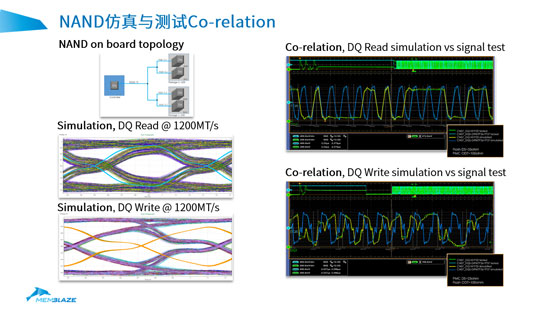

SSD从采用DDR接口开始,信号完整性的仿真就已经是标准配置,尤其是在Gbps以上的信号速率,没有仿真寸步难行。所以信号完整性仿真是必须要覆盖的设计项目,用以确定前期的拓扑方案,驱动和端接选择。

仿真之后需要进行测试,由于测试本身存在局限性,如测试点的位置确定,测试覆盖率等,使得测试无法成为系统信号完整性的直接证明。所以需要通过仿真与测试的Co-relation对比,来验证仿真结果与最终实现的一致性,从而确定最终的仿真模型,并在此基础上进行整板全信号仿真,以覆盖所有的信号。

除了信号之外,需要重视电源完整性对信号完整性的影响,滤波电路的选取,电源的设计与测量结果,也是影响信号质量的直接因素。

如上图所示,左侧图例是对一组总线挂接两颗NAND,ODP+ODP的读写信号仿真结果,速率在1200Mbps。

而右侧图例所示,是NAND读写信号的测试点测试结果,以及根据对测试点的信号仿真,提取仿真波形,最终与测试波形进行拟合。拟合成功则认为仿真模型的结果与实际实现相匹配,那么需要在这个仿真模型下,再进行全信号的总线仿真,以确保覆盖所有信号的完整性评估。

最后,我们还总结出了一些常用的,可以进一步调优信号完整性,评估信号可靠度裕量的手段:

以上是Memblaze在长江存储2022晶栈Xtacking线上沙龙企业级专场,针对NAND接口速率对高性能SSD硬件设计带来的挑战与应对的一些总结。Memblaze始终以打造高性能、高可靠性企业级SSD为己任,致力于推动国产企业级SSD发挥更大价值。本次演讲只是一个开始,更多精彩,敬请期待!