接口速度决定SSD的性能上限。如今,PCIe SSD正进入PCIe 4.0时代,并向速度更快的PCIe 5.0进发。为避免PCIe链路以较低的速率工作导致PCIe SSD性能下降(如PCIe 4.0的SSD以PCIe 1.0速率工作),自PCIe 2.0开始,PCIe SSD在初始化过程中,会在链路训练(Link Training)阶段进行链路信号质量、速率、链路宽度的调节,它由链路训练状态机(Link Training and Status State Machine,以下简称LTSSM)自动完成。

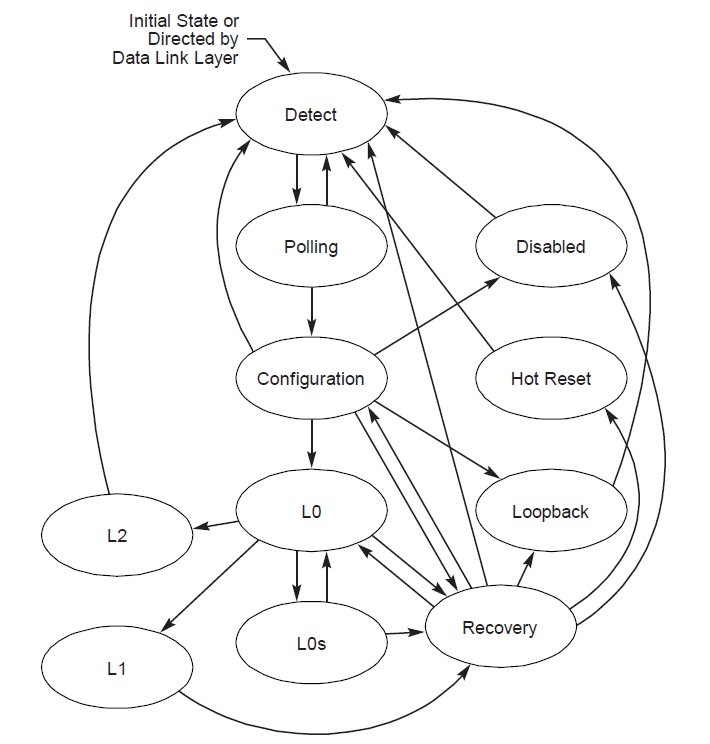

LTSMM的主要状态(From PCIe Spec)

如上图所示,LTSSM一共有11个状态,当系统启动或复位等情况发生,PCIe会从Detect开始,经Polling、Configuration进入L0,并正式开始用户指令和数据的传输。

在首次进入L0的过程中,PCIe设备始终工作在2.5GT/s的传输速率;进入L0后,如果PCIe两端设备均支持更高的速率,则会进入Recovery状态。该状态允许设备变更信号的传输速率,重新进行Bit Lock、Symbol Lock或Block Alignment、信号极性翻转等操作,并进行信号质量的调节。此外,当设备从L0s、L1状态退出,以及链路出现错误等情况发生时,也会进入Recovery状态。

对PCIe 2.0来说,由于信号速率相对较低,它只需要在首次进入L0后,再以5GT/s的速率重新进行Bit Lock、Symbol Lock、信号极性翻转等操作,即可满足速率和信号质量的要求。

而对于PCIe 3.0和更高速率来说,则需要在Recovery状态进行名为“Equalization Procedure”的均衡过程。此过程中PCIe链路两端端口——Downstream Port(主机)和Upstream Port(如PCIe SSD)会通过TS报文相互协商信号参数,以达到最佳的链路状态。

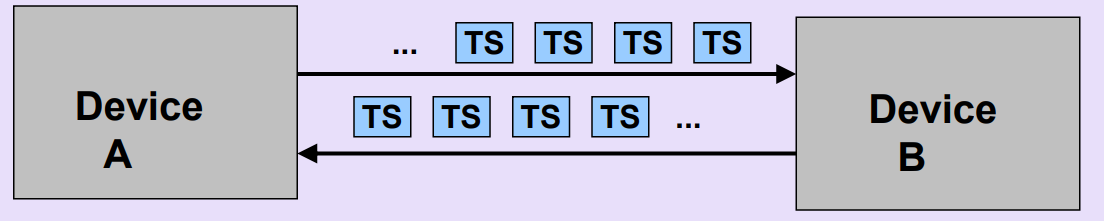

(from PCI-SIG)

TS报文(Training Sequence)是PCIe设备进行链路训练的重要依据,如前面提到的位锁定、字符锁定、块对齐、通道号等。TS报文中的Symbol 6到Symbol 9包含了均衡过程所需的重要物理层参数设定,如Tx预设,FS、LF或Pre-Cursor、Cursor、Post-Cursor等,它们都是影响信号质量的重要参数,可在提高信号速率的同时,降低误码率。

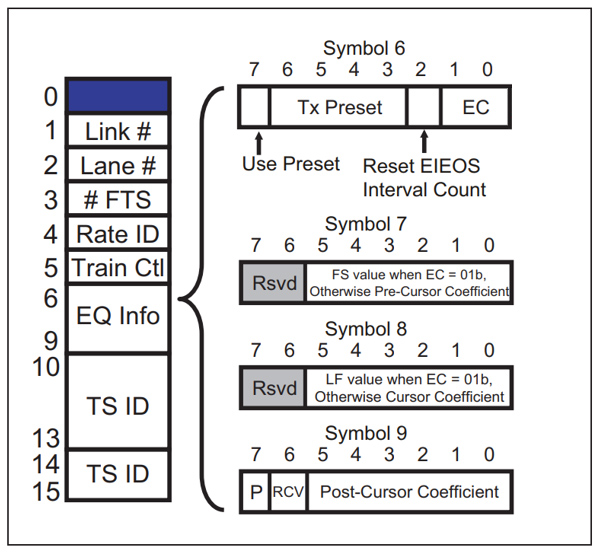

TS数据报文构成(From Mindshare <PCI Express Technology>)

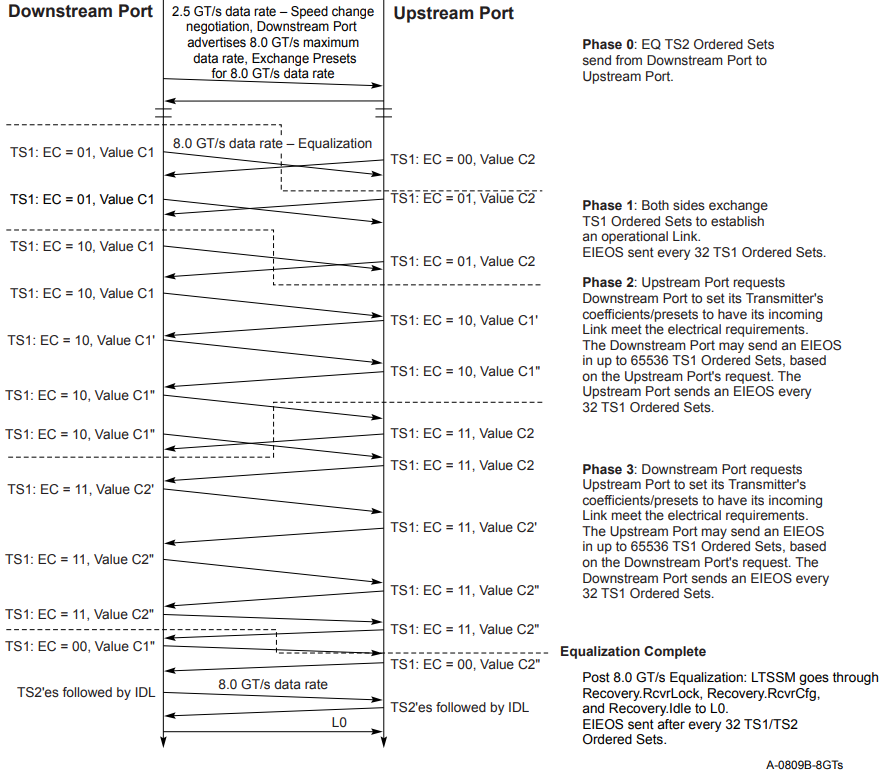

Equalization Procedure分为4个阶段,Phase 0至Phase 3,具体流程如下:

2.5GT/s切换到8GT/s流程示例(from PCIe spec)

以上图为例,当Downstream Port(主机)准备从2.5GT/s切换到8GT/s时,它就会向Upstream Port(如PCIe SSD)以2.5GT/s速率发送带有起始预设的TS2数据报文。Upstream Port在接收到该报文后会按照要求设置自己的预设参数,然后发送TS1报文给Downstream Port。

例外情况:当链路重新进行均衡,PCIe两端设备已经处在最高速率状态,此时不需要经过Phase 0,而是直接进入Phase 1;对于速率更高的PCIe 6.0,则需要从32GT/s速率重新进行均衡。

在Phase 1阶段中,Upstream Port和Downstream Port通过交换FS、LF信息,来确定Tx系数的上限和下限——Downstream Port在接收到Upstream Port发来的TS1报文后,会进入到Phase 1并以8GT/s发送EC = 01b的TS1报文;Upstream Port会评估接收到的信号,一旦能够识别到2个连续的8GT/s的TS1报文(这意味着误码率已经低于10-4),也会进入到Phase 1,开始以8GT/s的速率发送EC = 01b的TS1报文。Downstream Port在接收到Upstream Port发出的EC=01b的TS1报文后,表明初步的提速和信号优化工作已经完成。

接Phase 1:当Downstream Port接收到Upstream Port发出的EC=01b的TS1报文后,会进入Phase 2阶段,开始发送EC=10b的TS1报文;当Upstream Port也回复了EC=10b的TS1报文,表明两个Port都进入了Phase 2。

在Phase 2阶段中,将进行Downstream Port的信号质量优化工作,降低链路的误码率:Upstream Port会要求Downstream Port进行Tx参数,如boost、pre-shoot、de-emphasis的设定,以满足Upstream Port端对于信号电气质量的要求。

Downstream Port在接收到请求后会进行相应设定并发送TS1报文,Upstream Port在接收到报文后会对其信号质量加以评估,如果误码率无法满足小于10-12,则会向Downstream Port提出新的Tx参数设定,如此往复,直到Downstream Port的信号质量能够满足要求。

在Phase 3阶段中,将进行Upstream Port的信号质量优化工作,方法和Phase 2相同:Upstream Port按照Downstream Port提出的参数设定自己的Tx参数,然后发送TS1报文。Downstream Port评估接收到的TS1报文是否满足小于10-12误码率,如果不满足则提出新的Tx设定请求,如此往复,直到Upstream Port的信号质量能够满足要求。

至此,均衡过程的4个阶段就都完成了。需要指出的是,Phase 2和Phase 3是可选的,如果跳过这两个阶段,会加速PCIe链路的初始化,但会以数据准确性为代价。

一般来说,PCIe链路速率达到PCIe 3.0之后,如果链路两边端口都支持PCIe 4.0,那么可以再进行一次均衡过程。

但是,随着速率级别的越来越高,如果始终以一级一级的提速方式进行均衡,无疑会浪费大量的时间,并让初始化过程变得冗长。

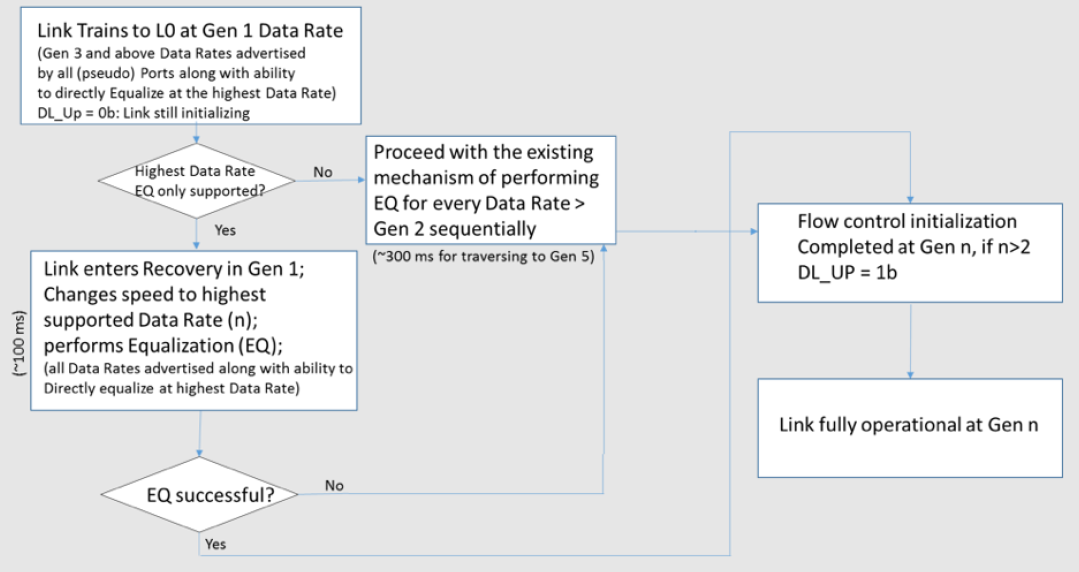

Bypassing Equalization流程(from PCIe 5.0 spec)

在PCIe 5.0规范中,加入了Bypassing Equalization功能(如上图所示),如果链路两端设备均支持该能力,那么可以跳过中间态,直接进行32GT/s的均衡过程,并达到最高速率和信号质量,即2.5GT/s、5GT/s → 32GT/s;如果Bypassing Equalization失败,则需要一级一级向上训练,直到达到最高速率。

而对于PCIe 6.0,则需要经过32GT/s中间态,可由2.5GT/s或5GT/s,经32GT/s再提升至64GT/s。